For exclusive use of adopters of the book *Digital Design Principles and Practices*, Fourth Edition, by John F. Wakerly, ISBN 0-13-186389-4.

- 3.3 A logic buffer is a non-linear amplifier that maps the entire set of possible analog input voltages into just two output votages, HIGH and LOW. An audio amplifier has a linear response over its specified operating range, mapping each input voltage into an output voltage that is directly proprtional to the input voltage.

- 3.6 From the American Heritage Electronic Dictionary (AHED), copyright 1992 by Houghton Mifflin Company:

- (1) A structure that can be swung, drawn, or lowered to block an entrance or a passageway.

- (2) a. An opening in a wall or fence for entrance or exit. b. The structure surrounding such an opening, such as the monumental or fortified entrance to a palace or walled city.

- (3) a. A means of access: the gate to riches. b. A passageway, as in an airport terminal, through which passengers proceed for embarkation.

- (4) A mountain pass.

- (5) The total paid attendance or admission receipts at a public event: a good gate at the football game.

- (6) A device for controlling the passage of water or gas through a dam or conduit.

- (7) The channel through which molten metal flows into a shaped cavity of a mold.

- (8) Sports. A passage between two upright poles through which a skier must go in a slalom race.

- (9) Electronics. A circuit with multiple inputs and one output that is energized only when a designated set of input pulses is received.

Well, definition (9) is closest to one of the answers that I had in mind. The other answer I was looking for is the gate of a MOS transistor.

- 3e3.14 3.16 A CMOS inverting gate has fewer transistors than a noninverting one, since an inversion comes "for free."

- 3.19 One way is that a romance could be sparked, and the designers could end up with a lot less time to do their work. Another way is that the stray perfume in the IC production line could have contaminated the circuits used by the designers, leading to marginal operation, more debugging time by the deidicated designers, and less time for romance. By the way, the whole perfume story may be apocryphal.

- 3.20 Using the maximum output current ratings in both states, the HIGH-state margin is 0.69 V and the LOW-state margin is 1.02 V. With CMOS loads (output currents less than 20 μA), the margins improve to 1.349 V and 1.25 V, respectively.

- 3.22 The first answer for each parameter below assumes commercial operation and that the device is used with the maximum allowable (TTL) load. The number in parentheses, if any, indicates the value obtained under a lesser but specified (CMOS) load.

$V_{\text{OHmin}}$  3.84V (4.4V)

$V_{\text{IHmin}}$  3.15 V

$V_{\rm IL,max}$  1.35 V

$V_{\rm OLmax}$  0.33 V (0.1 V)

$I_{\rm Imax}$  1  $\mu$ A

$I_{\rm OLmax}$  4 mA (20  $\mu$ A)

$I_{\rm OHmax}$  -4 mA (-20  $\mu$ A)

- 3.24 (Note typo in the first printing; change "2.0–5.0 V" to "3.15–5.0 V.") The specification for the 74HC00 shows a maximum power-supply current of 10  $\mu$ A when the inputs are at 0 or 5V, but based on the discussion in Section 3.5.3 we would expect the current to be more when the inputs are at their worst-case values (1.35 or 3.15V). If we consider "nonlogic" input values, the maximum current will flow if the inputs are held right at the switching threshold, approximately  $V_{\text{CC}}/2$ .

- 3.26 Using the formulas on page 120, we can estimate that  $R_{\rm p(on)}=(5.0-3.84)/0.004=290\Omega$  or, using the higher value of  $V_{\rm OHmin}$  in the spec, that  $R_{\rm p(on)}=(5.0-4.4)/0.00002=30{\rm K}\Omega$ . (The discrepancy shows that the output characteristic of this device is somewhat nonlinear.) We can also estimate  $R_{\rm n(on)}=0.33/0.004=82.5\Omega$ .

For exclusive use of adopters of the book *Digital Design Principles and Practices*, Fourth Edition, by John F. Wakerly, ISBN 0-13-186389-4.

- 3.39 Smaller resistors result in shorter rise times for LOW-to-HIGH transitions but higher power consumption in the LOW state. Stated another way, larger resistors result in lower power consumption in the LOW state but longer rise times (more ooze) for LOW -to-HIGH transitions.

- 3.42 The wired output has only passive pull-up to the HIGH state. Therefore, the time for LOW-to-HIGH transitions, an important component of total delay, depends on the amount of capacitive loading and the size of the pull-up resistor. A moderate capacitive load (say, 100 pF) and even a very strong pull-up resistor (say,  $150\Omega$ ) can still lead to time constants and transition times (15 ns in this example) that are longer than the delay of an additional gate with active pull-up.

- 3e3.42 3.43 The winner is 74FCT-T—48 mA in the LOW state and 15 mA in the HIGH state (see Table 3–8). TTL families don't come close.

- 3e3.46 3.47 *n* diodes are required.

- 3.50 LS-TTL output driving the input. Since  $I_{\rm ILmax}=0.4{\rm mA}$ , we get  $R_{\rm pd}=0.5/0.004=1250\Omega$  and  $P_{pd}=V_{\rm IL}^2/R_{\rm pd}=(0.5)^2/1250=0.2{\rm mW}$ . (Alternatively,  $P_{\rm pd}=V_{\rm IL}I_{\rm IL}=0.5\cdot0.0004=0.2{\rm mW}$ ) For the pull-up, we must have at most a 2.3-V drop in order to create a  $V_{\rm IH}$  that is no worse than a standard LS-TTL output driving the input. Since  $I_{\rm IHmax}=20\mu{\rm A}$ , we get  $R_{\rm pu}=2.3/0.00002=115{\rm k}\Omega$  and  $P_{\rm pu}=V_{\rm IH}^2/R_{\rm pu}=(2.3)^2/115000=0.046{\rm mW}$ . (Alternatively, we could have calculated the result as  $P_{\rm pu}=V_{\rm IH}I_{\rm IH}=2.3\cdot0.00002=0.046{\rm mW}$ .) The pull-up dissipates less power.

- 3.52 The main benefit of Schottky diodes is to prevent transistors from saturating, which allows them to switch more quickly. The main drawback is that they raise the collector-to-emitter drop across an almost-saturated transistor, which decreases LOW -state noise margin.

- 3.64 TTL-compatible inputs have  $V_{\rm IHmin} = 2.0 \, \rm V$ , and typical TTL outputs have  $V_{\rm OHmin} = 2.7 \, \rm V$ . CMOS output levels are already high compared to these levels, so there's no point in wasting silicon to make them any higher by lowering the voltage drop in the HIGH state.

For exclusive use of adopters of the book *Digital Design Principles and Practices*, Fourth Edition, by John F. Wakerly, ISBN 0-13-186389-4.

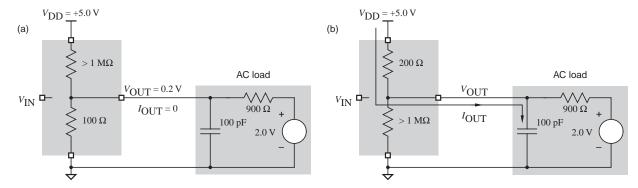

3.69 Rise time can be calculated in a manner similar to the solution of Exercise 3.68. Part (a) of the figure below shows the conditions in the circuit when the output is in a steady LOW state with  $V_{\rm OUT}=0.2\,\rm V$  as predicted in Exercise 3.68. If at time t=0 the CMOS output changes to the HIGH state, the situation depicted in (b) results. The Thévenin equivalent of the voltage source and the two resistors in the HIGH state is  $163.6\Omega$  in series with a  $4.545-\rm V$  voltage source.

$V_{\rm OUT}$  cannot change instantly, but at time  $t=\infty$ , the capacitor will be charged to the Thévenin -equivalent voltage of 4.545 V. Until then, the value of  $V_{\rm OUT}$  in between is governed by an exponential law:

$$\begin{split} V_{\rm OUT} &= 0.2 \text{V} + (4.545 - 0.2 \text{V}) \cdot (1 - e^{-t/R_{\rm p}C_{\rm L}}) \\ &= 0.2 \text{V} + 4.345 \cdot (1 - e^{-t/163.6 \cdot 100 \cdot 10^{-12}}) \text{V} \\ &= 0.2 \text{V} + 4.345 \cdot (1 - e^{-t/16.36 \cdot 10^{-9}}) \text{V} \end{split}$$

The RC time constant in this case is 16.36 ns. To obtain the rise time, we must solve the preceding equation for  $V_{\text{OUT}} = 1.5$  and  $V_{\text{OUT}} = 3.5$ , yielding

$$t = -16.36 \cdot 10^{-9} \cdot \ln \frac{4.545 - V_{\text{OUT}}}{4.356}$$

$$t_{1.5} = 5.82 \text{ ns}$$

$$t_{3.5} = 23.35 \text{ ns}$$

The rise time  $t_T$  is the difference between these two numbers, or 17.53 ns. Although the time constant is shorter than in Section 3.6.1, the asymptote of 4.545 V is appreciably closer to the threshold than the 5-V asymptote in Section 3.6.1, so the rising edge starts slowing sooner, and the overall rise time is slightly longer than the 17-ns result in Section 3.6.1 (as suggested in the solution to Exercise 3.67).

3e3.70 3.70 The time constant is  $1 \text{k}\Omega \cdot 50 \text{ pF} = 50 \text{ ns}$ . We solve the rise-time equation for the point at which  $V_{\text{OUT}}$  is 1.5 V, as on p. 119 of the text:

$$t_{1.5} = -50 \cdot 10^{-9} \cdot \ln \frac{5.0 - 1.5}{5.0}$$

$t_{1.5} = 17.83 \text{ ns}$

3.79 The LSB toggles at a rate of 16 MHz. It takes two clock ticks for the LSB to complete one cycle, so the transition frequency is 8 MHz. The MSB's frequency is 2<sup>7</sup> times slower, or 62.5 KHz. The LSB's dynamic power is the most significant, but the sum of the transitions on the higher order bits, a binary series, is equivalent to almost another 8 MHz worth of transitions on a single output bit. Including the LSB, we have almost 16 MHz, but applied to the load capacitance on just a single output. If the different ouputs actually have different load capacitances, then a weighted average would have to be used.

For exclusive use of adopters of the book *Digital Design Principles and Practices*, Fourth Edition, by John F. Wakerly, ISBN 0-13-186389-4.

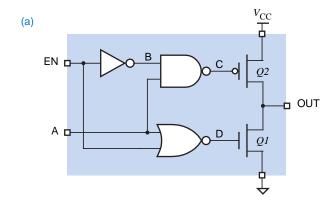

## 3e3.81 3.83

| (b) |    |   |   |   |   |           |            |      |

|-----|----|---|---|---|---|-----------|------------|------|

| (2) | EN | Α | В | С | D | Q1        | <i>Q</i> 2 | OUT  |

|     |    |   |   |   |   | on<br>off |            |      |

|     | _  |   |   | _ | _ | off       |            |      |

|     | Η  | Н | L | Η | L | off       | off        | Hi-Z |